pcie2_ddr3_usb30_virtex6

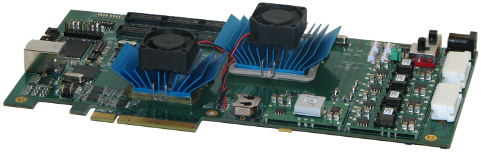

Płyta pcie2_ddr3_usb30_virtex6 evaluation board jest to już kolejne rozwiązanie z serii płyt ewaluacyjnych projektowanych na potrzeby zaawansowanych projektów opartych o IP Core’y. Podstawowym założeniem konstrukcyjnym płyty było zaprojektowanie rozwiązania składającego się z dwóch układów FPGA połączonych między sobą, otoczeniem i peryferiami bardzo szybkimi interfejsami wymiany danych. Płyta jako całość zaprojektowana została jako akcelerator symulacji elektronicznej dla projektów złożonych systemów typu embedded. Wygląd płyty po zmontowaniu przedstawiono na rysunku:

Parametry płyty

Parametry płyty

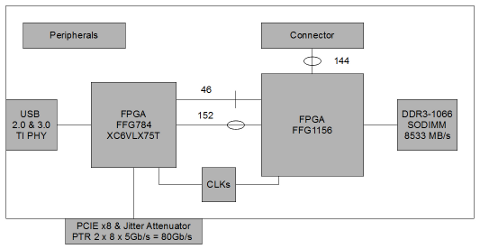

Budowa płyty to dwa układy FPGA firmy Xilinx z serii Virtex-6. Interfejs PCI-Express 2.0, Interfejs USB Super Speed 3.0 i interfejs DDR3-1066. Pozostałe peryferia mają charakter pomocniczy. Uproszczony schemat płyty przedstawiono na rysunku:

Projekt płyty to 16-sto warstwowa płyta PCB która zawiera dwa układy FPGA firmy Xilinx oraz peryferia które razem tworzą system o następującej konfiguracji:

- Główny (ale nie największy) układ FPGA to XC6VLX75T-2FF784C. Jest to centralny układ FPGA zapewniający komunikację z otoczeniem poprzez interfejsy USB i PCIE oraz odpowiedzialny jest za dynamiczną rekonfigurację drugiego układu FPGA pełniącego rolę właściwego układu obliczeniowego akceleratora

- Układ obliczeniowy to XC6VLX240T-2FFG1156 lub inny w kompatybilnej obudowie 1156 kulkowej. Odpowiedzialny za wykonywanie właściwej akceleracji zadanych obliczeń. Do układu bezpośrednio połączony jest interfejs pamięci DDR3 oraz interfejs złącza zewnętrznego używanego do podpięcia adapterów usprawniających proces symulacji

- USB3.0 Device. Warstwa fizyczna TUSB1310A wspierająca tryby pracy USB Super-Speed (5Gb/s) oraz standardowo interfejsy wolniejsze

- PCIE x8. Interfejs do magistrali PCI-Express. Płytę zaprojektowano do wspierana standardu 2.0 o szerokości 8 par nitek sygnałowych

- Moduł pamięci DDR3 SODIMM o pełnym podpięciu wszystkich linii modułu do układu FPGA. Przepustowość połączeń zaprojektowane do wspierania najszybszych transferów oferowanych przez dostępne na rynku moduły pamięci ograniczonych jedynie wydajnością układu FPGA

- Interfejsy użytkownika i systemowy wymiany danych pomiędzy układami FPGA. Interfejs użytkownika to 76 linii różnicowych projektowanych przede wszystkim jako 76 bardzo szybkich linii z interfejsem LVDS, które mimo wszystko mogą pracować jako linie single-ended dostarczając wówczas 152 linii łączących obydwa układy. Interfejs systemowy to dedykowany 46-liniowy interfejs akceleratora podpięty do linii systemowych obliczeniowego układu FPGA. W przypadku różnicowych linii LVDS każda z nich pracująca jako DDR LVDS ma prędkość transmisji 1,3Gb/s

- Zewnętrzny interfejs w postaci złącz oferujący interfejs wymiany danych pomiędzy obliczeniowym układem FPGA a zewnętrznymi adapterami. Ilość linii dla single-ended to 144 oraz 77 dla LVDS

- CLK’s. System zegarów zapewniający taktowanie układów FPGA i innych peryferii. Zastosowano zestaw konfigurowalnych i stałych zegarów. Dodatkowo na potrzeby PCIE oraz USB3.0 zastosowano tłumiki jitter'a. Zastosowane zegary umożliwiają uzyskanie zegarów w zakresie częstotliwości do 700MHz

- Peripherals. Podstawowe peryferia takie jak DIP-Switch'e, Diody LED i jumpery na potrzeby ustawień konfiguracyjnych i monitorowania stanu pracy systemu

- Zasilanie. Płytę wyposażono w 10 konwerterów napięć z których najbardziej wydajnym jest 22-amperowy moduł 1V

Interfejsy:

Specyfikacja wejściowa

Postawione wymagania:

Przedstawione parametry płyty określają co zostało zrobione. Przedstawione jednak zostanie jak to wyglądało od strony realizacji projektu. Na wstępie opisane zostaną bardzo okrojone wymagania obrazują jaki był punkt wyjścia dla projektu tej płyty. Na jej podstawie miało powstać rozwiązanie które spełniałoby wszystkie szczegółowe wymagania postawione przez zleceniodawcę i jak wynika z testów zostały spełnione z naddatkiem. A oto wymagania, oczywiście bardzo okrojone:

-

Budowa dwu-układowa

- Zwarta konstrukcja. Płyta musiała mieć rozmiar nie większy niż narzucony przez zleceniodawcę

- Interfejsy komunikacji ze światem USB i PCI-Express

- Interfejs pamięciowy najlepiej DDR2 lub DDR3 64 bitowy

- Szybki interfejs pomiędzy układami FPGA

- Szybki interfejs zewnętrzny ogólnego przeznaczenia

- Uniwersalność zasilania

- Podstawowy zestaw peryferii

Osiągnięto to w następujący sposób:

- System ma budowę dwu-układową. Dzięki temu rozwiązaniu pierwszy układ dostarczany jest jako na stałe zaprogramowany układ FPGA obsługujący interfejsy USB i PCIE. Dzięki opracowanemu systemowi istnieje możliwość reprogramowania obliczeniowego układu FPGA w zależności od aktualnie wykonywanej akceleracji

- Zwarta konstrukcja, wymaganie teoretycznie proste do realizacji narzuciło dużo ograniczeń które na szczęście dało się wyeliminować osiągając postawione cele. Sprawny projektant od razu zauważy, że stopień złożoności projektu umożliwia redukcję rozmiaru płyty o ok. 30%. Owszem, tym razem jednak narzucony czas realizacji projektu, koszty a przede wszystkim wydajność połączeń sprawiły, że wymiary płyty stanowiły pewnego rodzaju utrudnienie

- Zastosowane interfejsy wymiany danych z otoczeniem. Użyto dwóch w naszej ocenie najlepszych dla tego typu rozwiązań. PCI-Express i USB. W obu przypadkach najszybsze możliwe do zaimplementowania wersje. W przypadku PCI-E można owszem użyć wersję x16 jednak w praktycznych rozwiązaniach stosuje się maksymalnie x8. Podyktowane to jest głównie zasobami które dostarczają producenci układów FPGA, z tego też powodu płytę zaprojektowano zgodnie z interfejsem PCIE gen 2 a nie gen 3. W przypadku USB użyto oczywiście USB3.0 który to interfejs w czasie projektu tej płyty był bardzo pionierskim rozwiązaniem ze względu na ogólny brak gotowych rozwiązań

-

Interfejs pamięciowy to DDR2 lub DDR3. Zdecydowano się na DDR3 ze względu na jeszcze szybsze transfery jakie można uzyskać dzięki tego typu zastosowanej pamięci. Wybór ten jednak dostarczył szereg nowych wyzwań narzucających np. wymaganą dokładność wewnątrz linii DQS na poziomie 5ps przy czym czas propagacji przelotki na tych liniach to upraszczając 25ps. Interfejs ten, podobnie jak PCIE musiały więc mieć uwzględnione takie czynniki wpływające na czas propagacji (nie tylko) jak:

- Indywidualny czas propagacji każdego wyprowadzenia pomiędzy kulka układu FPGA a strukturą krzemową

- Czas propagacji inny dla warstwa zewnętrznych i wewnętrznych na PCB

- Budowa gwiazdowa niektórych połączeń a rzeczywisty czas propagacji pomiędzy węzłami połączenia

- Zmienny rzeczywisty czas propagacji w zależności od sposobu prowadzenia połączeń. Aspekt ten obejmuje powstałe inne parametry ścieżki o stałej długości w zależności czy jest prostym połączeniem czy spiralą

- Wzajemne sprzężenia pomiędzy ścieżkami na danej warstwie i pomiędzy warstwami. W zastosowanej technologii PCB o wiele łatwiej było zakłócić ścieżkę sygnałem ze ścieżki znajdującej się na innej warstwie niż sygnałem ze ścieżki z na tej samej warstwie co ścieżka zakłócana

- Interfejs pomiędzy układami FPGA. Ze względu na to, że większy układ to właściwy układ obliczeniowy, a układ mniejszy to tylko układ kontrolny, wymagane było połączenie tych układów interfejsem o przepustowości znacznie większej niż zastosowane interfejsy zewnętrzne. Cel oczywiście osiągnięto, a dzięki szerokiej magistrali odbiorca płyty nie musi multipleksować kierunku transmisji danych na magistrali, co znacznie ułatwia projekt wzajemnego połączenia układów i oczywiście dostarcza połączenie typu full-dupleks co wiąże się z podwojeniem prędkości transmisji łącza

- Zasilanie płyty to bardzo wydajne źródła zasilania, które z kilku ważnych powodów zbudowano jako moduły mogące dostarczyć znacznie więcej prądu niż to wymaga system. Wydawać się może, że przy projekcie takich systemów zasilanie to problem drugorzędny. Niestety jest to jedno z większych wyzwań tego typu projektów. Jest tak z powodów takich jak:

- Wymagana wydajność prądowa i stabilność napięcia zasilania

- Wymagana stromość narastania napięć zasilających przy starcie systemu i problem „przenikania” jednych napięć zasilających dany układ do innych linii zasilających. Problem wymuszony specyfikacją zastosowanych układów FPGA jak i ze względu na jakość zasilania, dużą ilością zastosowanych kondensatorów o wyjątkowo małym ESR

- Jakość zasilania w sensie szumów i zakłóceń przenoszonych przez zasilanie. Niektóre sekcje musiały byś zasilane przez bardzo rozbudowany układ filtrujący który jednocześnie ułatwiając jak i utrudniając projekt wymagały użycia liniowych stabilizatorów napięcia

- Izolacja napięciowa. Zastosowane 16 warstw przy 62 milsach grubości płyty spowodowały, że sposób prowadzenie zdolnych przenieść wiele amperów ścieżki z potencjałem 12V..1V było pewnym problem którego nie uwzględnienie znacznie zwiększyłoby różnicę potencjałów pomiędzy sąsiadującymi obszarami różnych potencjałów. Płytę więc projektowano w sposób w który ewentualne przebicie ma nie uszkodzić układów a jedynie wywołać ogólne zwarcie zasilania. Wszystkich zagrożeń nie wyeliminowano i nie taki był cel projektu, jednak ten ponadplanowy cel stanowił ćwiczenie mające przygotować projektantów do projektów systemów o wiele bardziej zaawansowanych w kwestii odporności na niszczące system zewnętrzne zakłócenia EMC

Ze względu na tajemnicę handlową w artykule nie myło możliwości przedstawienia wielu bardzo ciekawych aspektów konstrukcyjnych płyty takich jak schematy, niektóre zastosowane nowatorskie rozwiązania czy widok szczegółowy płyty