DDR2

Podobnie problem wygląda w przypadku połączenia układu FPGA z pamięciami DDR2 SODIMM. Kompletnie zroutowany układ ma postać:

W tym przypadku dwie sąsiadujące warstwy posiadają następujący topologie połączeń:

W przypadku DDR2 wymagania co do jakości połączeń powodują, że pojedyncza przelotka na linii sygnałowej wprowadza offset na linii który dla najszybszych pamięci wykracza poza dopuszczalne wartości.

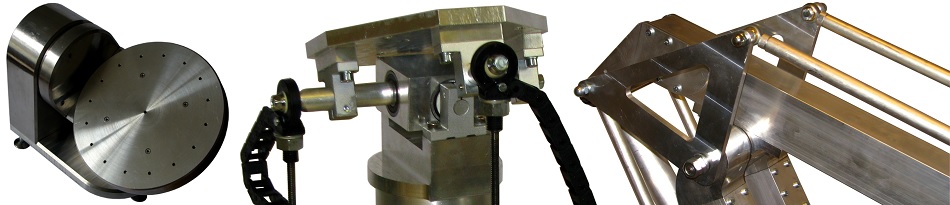

Ze względu na inny typ układów dodatkowych FPGA i inną ich obudowę nie było możliwe wykorzystanie wykonanego routowania dla układu podstawowego dla interfejsu DDR2. Konieczne było zaprojektowania topologii ścieżek od nowa. Osiągnięty efekt ma postać:

W przypadku wszystkich przedstawionych tu interfejsów DDR2 widać liczne kondensatory blokujące na napięciu zasilania, odniesienia i referencyjnym dla połączenia DDR2-FPGA