Optymalizacja algorytmów w układach FPGA

Projektowanie wydajnych i bezbłędnych modeli na potrzeby układów FPGA wymaga dużego doświadczenia w projektowaniu modeli cyfrowych układów scalonych. Niestety nie da się na kilku stronach wyczerpać tego zagadnienia. Można jedynie wskazać najważniejsze sposoby, którymi należy się kierować przy projektowaniu modeli.

Projektant rozpoczynający pracę z układami FPGA z pewnością przyjmie założenie, że projektując model układu cyfrowego należy stosować się do zasady używania jak najmniejszej ilości rejestrów oraz minimalizowania ilości przesyłów między-rejestrowych. Niestety dla wydajnych modeli projektowanych z naciskiem na maksymalną częstotliwość pracy nie jest to zawsze prawdą. Jedną z metod przyspieszenia pracy układu jest zastosowaniu większej ilości rejestrów podczas wykonywania złożonych operacji. Wydawać się może, że ta droga nie jest właściwa, jednak dodanie pośrednich rejestrów przyśpiesza działanie układu. Wadą takiego rozwiązania są:

- zwiększenie wykorzystania zasobów układu FPGA

- opóźnienie w otrzymywaniu obliczanych wartości

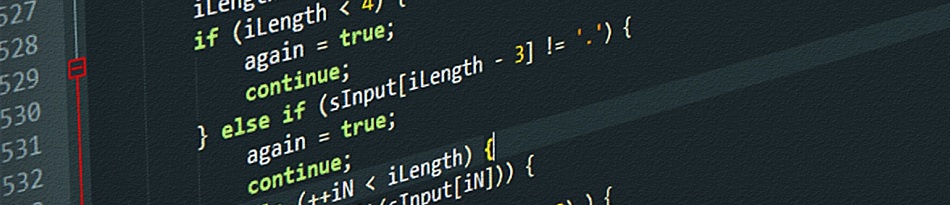

Dobrym przykładem jest moduł przedstawiony na listingu:

//Rozwiązanie pracujace z fmax 123MHz

always@(posedge clk)

begin

tmp0 <= din;

if (rst == 1'b1) begin

dout <= "00000000";

tmp0 <= "00000000";

end else begin

dout <= (tmp0 + "01010101")*3;

end

end//Rozwiązanie pracujace z fmax 163MHz

always@(posedge clk)

begin

tmp0 <= din;

if (rst == 1'b1) begin

dout <= "00000000";

tmp0 <= "00000000";

tmp1 <= "00000000";

end else begin

tmp1 <= tmp0 + "01010101";

dout <= tmp1 * 3;

end

end

W pierwszym przypadku operacja:

dout <= (tmp0 + "01010101")*3;

została rozłożona na dwie operacje:

tmp1 <= tmp0 + "01010101";

dout <= tmp1 * 3;

Jak widać wyliczenie nowej wartości dla wyjścia dout zajmuje teraz dwa takty zegarowe, jednak dzięki pośredniemu rejestrowi maksymalna częstotliwość pracy układu zwiększyła się z 123MHz do 163MHz.