Szerokość Licznika

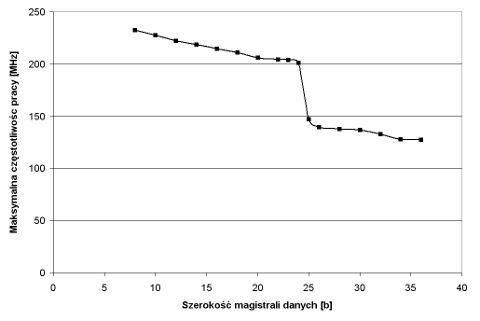

Poza ogólnymi zaleceniami projektowymi jakie najczęściej opisywane są w literaturze na temat języka Verilog bardzo interesującym sposobem na przyspieszenie pracy układu jest takie zaprojektowanie licznika aby mieścił się w jednym bloku CLB. Dla układów Spartan2 maksymalna szerokość licznika to 24 bity. Powyżej tej wielkości, górna graniczna częstotliwość pracy układu spada skokowo ze względu na rozdzielenie logiki liczącej na przynajmniej dwa oddzielne bloki. Poza opisaną przypadkiem istnieje również oczywista zależność, że zwiększając szerokość licznika zmniejsza się dopuszczalna maksymalna częstotliwość pracy przy której układ działa stabilnie. Na rysunku poniżej przedstawiono wykres zależności maksymalnej częstotliwości pracy licznika w funkcji szerokości magistrali danych licznika.

Wykres maksymalnej częstotliwości pracy licznika w funkcji szerokości magistrali danych

Jak widać na wykresie, po przekroczeniu 24 bitów maksymalna częstotliwość pracy licznika spadła o 50MHz. Dlatego też projektując układ warto poszukać alternatywnych rozwiązań, które nie wymagają magistral, które nie mieszczą się w jednym bloku CLB.