Routing

Przed przystąpieniem do routowania ścieżek pozostaje zapewnienie mechanizmu spełniającego wymagania czasowe projektu. W tym przypadku na podstawie czasu propagacji ścieżek, czasu przejścia pomiędzy warstwami, zmiennego czasu propagacji sygnału z pinu układu do jego wewnętrznej struktury i wielu innych przygotowano dla wszystkich krytycznych połączeń ścieżki kompensujące zapewniające stałą propagację sygnału dla danego interfejsu. Realizowane jest to w postaci automatycznie generowanych ścieżek widocznych na rysunku poniżej. W tym celu opracowano własny program który ingerował w plik projektu umieszczając w nim ścieżki o odpowiednich parametrach.

Jak widać wchodzą one w skład danego NETu jednak nigdy nie mogą zostać zroutowane. Dodatkowo w końcowym etapie projektowania muszą zostać usunięte z projektu.

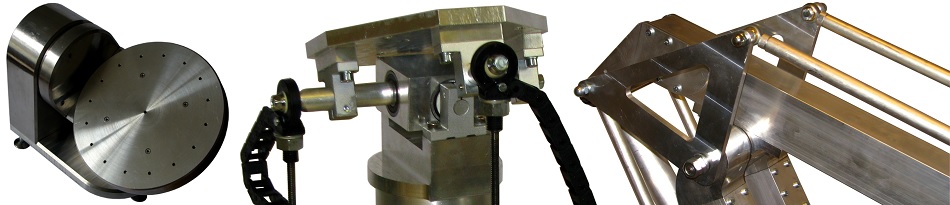

W tak przygotowanym projekcie czas rozpocząć routowanie ścieżek. Po wielu kolejnych przybliżeniach otrzymuje kompletnie połączone elementy których widok dla tej płyty przedstawiono na kolejnych zdjęciach:

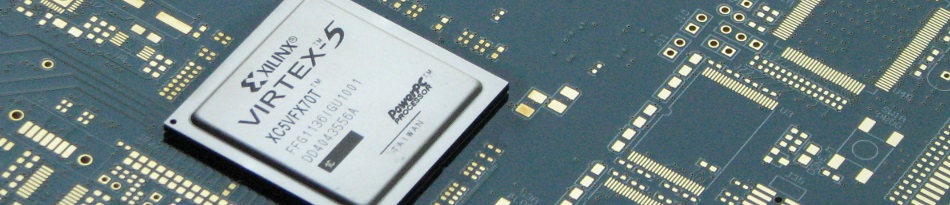

Routing głównego układu FPGA. Lewą część stanowi SuperSpeed'owy interfejs cyfrowy do układu USB3.0. Wyraźnie widać wyrównania ścieżek w celu zapewnienia zapewnienia właściwego czasu propagacji.