You are hereLogic Analyzer GUI

Logic Analyzer GUI

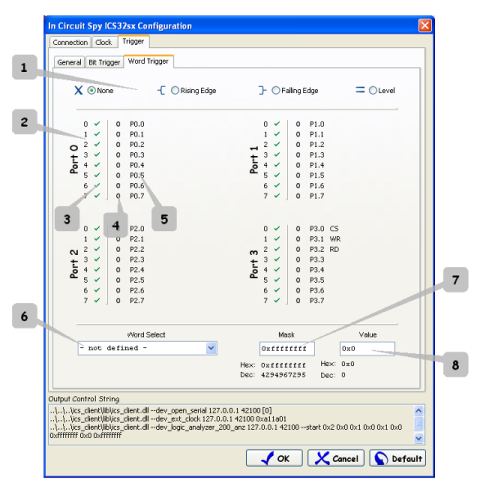

ICS32sx wyzwalanie słowem

Okno to umożliwia skonfigurowanie parametrów wyzwalania słowem Analizatora Stanów Logicznych. Dostępne ustawienia to "Tryb Wyzwalania" i "Maska i Wartość" słownego warunku wyzwalania. Wyzwalanie Słowem można scharakteryzować jako operacja "AND". Dokładniejsze wyjaśnienie tego pojęcia umieszczono w dalszej części dokumentu.

Sekcje zaznaczone na rysunku:

- Tryb Wyzwalania. Określa metodę interpretacji pojawienia się Słownego Warunku Wyzwolenia (SWW). Pojawienie się SWW rozumiane jest jako zależność polegająca na uwzględnieniu podczas analizy wyłącznie bitów wejścia pomiarowego dla których odpowiedni bit Maski przyjmuje wartość '1'. Następnie dla każdego z tych bitów porównywany jest stan odpowiedniej linii wejściowej z bitem pola Wartość. Gdy wszystkie bity mają obie wartości równe generowany jest wewnętrzny warunek zrównania. Następnie zrównanie to, w zależności od Trybu Wyzwalania, interpretowane jest następująco:

<>None. Brak ustawionego warunku wyzwalania.

UWAGA. Gdy Wyzwalanie Bitowe również jest ustawione jako None, wówczas analizator nie ma ustawionego warunku wyzwalania. W tym przypadku cykl pomiarowy to jednorazowe zapełnienie bufora wewnętrznego danymi wejściowymi

<> Rising Edge. W każdym cyklu zegarowym sprawdzane jest czy w poprzednim cyklu zegara taktującego system wystąpiło zrównanie się stanu wszystkich aktywnych linii wejściowych z wartościami ustawionymi w odpowiednich bitach parametru Wartość. Jeżeli w poprzednim cyklu brak było zrównania, a w bieżącym cyklu zrównanie to występuje, generowany jest wewnętrzny warunek wyzwolenia

<> Falling Edge. Podobnie jak w przypadku Rising Edge, z tą różnicą, że wewnętrzny warunek wyzwolenia generowany jest gdy w poprzednim cyklu zegarowym było zrównanie, a w bieżącym cyklu zegarowym zrównanie to już nie występuje

<> Level. Wewnętrzny warunek wyzwolenia generowany jest za każdym razem gdy występuje zrównanie się wszystkich aktywnych bitów.

Domyślnie przyjęte jest, że ustawienie Trybu Wyzwalania na np. Rising Edge polega na oczekiwaniu na pojawienie się stanu '0' do '1' na aktywowanej Maską linii wejściowej Analizatora. W przypadku analizy całego słowa, które w tym przypadku ma miejsce musi być realizowane inaczej. Przyjęto zasadę, że np. narastające zbocze zdefiniowane jest jako stan określony zależnością: (a) brak pojawienia się warunku wyzwolenia, (b) pojawienie się warunku wyzwolenia.Zasadę działania Wyzwalania Słowem można wytłumaczyć również na przykładzie:Ustawiono aktywne słowo w polu "Word Select". Słowo to zajmuje bity 8..15 z 32 bitowego wejścia pomiarowego analizatora. Wybierając w ten sposób słowo automatycznie uaktywnione zostały bity Maski (0x0000FF00). Parametr Wartość ustawiono na 0x4D. Po rozpoczęciu pomiaru każdorazowe pojawienie się na wejściu pomiarowym analizatora wartości 0xXXXX4DXX spowoduje wygenerowanie warunku wyzwolenia dla słowa. Jego interpretacja przez wewnętrzną logikę analizatora zależy od wybranego Trybu Wyzwalania. Znaki 'X' w tym przypadku oznaczają wartość dowolną - Numer bitu w danym porcie

- Maska Wyzwalania Słowem. Graficzny dostęp do poszczególnych bitów Maski. Maska ta po wybraniu słowa z pola "Word Select" domyślnie jest ustawiona na wszystkie bity danego słowa. Składowe bity słowa Maski można jednak zmieniać. Jest to szczególnie pomocne, gdy mając np. magistralę adresową potrzebne jest dodatkowo uchwycenie momentu, nie kiedy jest odwołanie pod dany adres ale kiedy następuje zapis danych pod dany adres. W tym przypadku uaktywnia się dodatkowo maskę sygnału zapisu i ustawia mu się Wartość na stan aktywny zapisu np. '0'. Innym przypadkiem zmiany bitów Maski słowa jest sytuacja gdy potrzebne jest uchwycenie odwołania do przestrzeni adresowej. W takim przypadku de-aktywuje się najmłodsze bity Maski w ilości zależnej od rozmiaru poddanej detekcji przestrzeni adresowej

- Wartość Wyzwalania Bitowego. Graficzny dostęp do poszczególnych bitów Wartości

- Nazwa Portu. Składa się z przynajmniej jednego członu (nazwy podstawowej) zawierającego 'P', numer portu i numer bitu w porcie. W przypadku gdy użytkownik zdefiniował sygnał bitowy i nadał mu nazwę, nazwa ta pojawia się obok nazwy podstawowej

- Word Select. Wybór słowa na podstawie którego zostanie wypełniona Maska warunku wyzwolenia. Lista sygnałów dostępna w tym polu jest identyczna z listą sygnałów zdefiniowanych przez użytkownika. Poza sygnałami użytkownika dostępny jest również sygnał "-- not defined --" obejmujący wszystkie dostępne bity maski

- Maska Wyzwalania bitowego. Reprezentacja liczbowa

- Wartość Wyzwalania Bitowego. Reprezentacja liczbowa

UWAGA. Graficzną reprezentację Maski i Wartości można zmieniać bez klikania myszą a jedynie przesuwaniem nad ikonami kursora myszy. W tym celu należy podczas tej operacji wcisnąć "Lewy Ctrl".

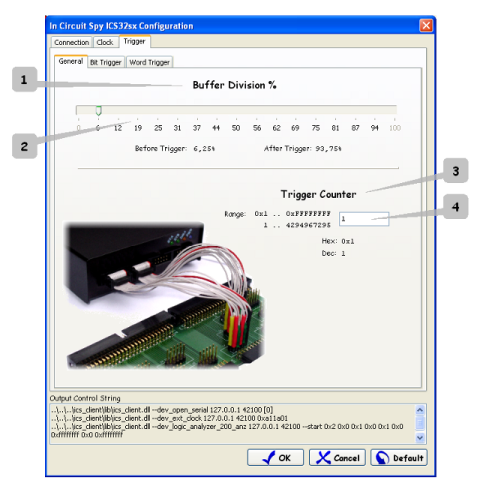

ICS32sx konfiguracja wyzwalania

Okno to umożliwia skonfigurowanie ogólnych parametrów wyzwalania Analizatora Stanów Logicznych. Dostępne ustawienia to "Podział Bufora" i "Licznik Warunków". Aby wyjaśnić znaczenie tych parametrów należy przestawić ogólną zasadę działania analizatora.

Analizator Stanów Logicznych ICS32sx posiada wewnętrzny bufor danych oparty o pamięć o skończonym rozmiarze, widzianą jednak jako bufor cykliczny. Po rozpoczęciu pomiaru bufor ten jest zapisywany danymi wejściowymi w takt zegara systemowego ustawianego w innej sekcji okna konfiguracji urządzenia. W przypadku braku aktywnego warunku wyzwalania bufor jest jednorazowo zapełniany danymi mierzonymi. W przypadku uaktywnienia warunku wyzwalania bufor stale zapełniany jest danymi wejściowymi do momentu aż spełniony zostanie przynajmniej jeden z warunków wyzwalania. W tym momencie bufor dopełniany jest danymi do momentu określonego przez parametr "Podział Bufora".

Zakładka konfiguracji podstawowych parametrów warunku wyzwalania przestawiona została na rysunku:

Sekcje zaznaczone na rysunku:

- Sekcja Buffer Division. W niej ustawiane jest miejsce w buforze, gdzie pojawi się warunek wyzwolenia

- Pole kontroli parametru "Buffer Division". Dostępne jest 15 różnych wartości. Każda z nich określa procentowy podział bufora na część przed i po pojawieniem się warunku wyzwolenia. Działanie tego parametru najlepiej jest przedstawić na przykładzie. Załóżmy, że ustawiono podział bufora na wartość 6 (6,25%). Dodatkowo ustawiono warunek wyzwalania na pojawienie się zbocza narastającego na jednej z linii wejściowych. Analizator został uruchomiony i trwa pomiar. Urządzenie wstępnie zapełniło wewnętrzny bufor i oczekuje na pojawienie się "zero na jeden" na wybranym wejściu. Po spełnieniu tego warunku bufor wewnętrzny zostaje zapełniony próbkami w ilości (100% - 6,25%) * rozmiar bufora. W wyniku tego ustawienia na ekranie ukaże się przebieg zawierający 6,25% danych widocznych przed warunkiem wyzwolenia i 93,75% po warunku. Samo przejście sygnału z zero do jeden powinno zostać uwidocznione w miejscu 6,25% bufora.

Jak łatwo się jest domyślić im mniejszą wartość ustawiamy dla tego parametru tym więcej danych jest rejestrowanych po wystąpieniu warunku wyzwolenia. Małe wartości parametru umożliwiają więc obserwację następstw wywołanych pojawieniem się warunku wyzwolenia. Duże wartości tego parametru z kolei przydatne są w sytuacji kiedy interesującą jest przyczyna, która uruchomiła warunek wyzwalania - Sekcja Trigger Counter. Odpowiedzialna za opóźnienie właściwego wyzwolenia analizatora o zadaną ilość zdarzeń powodujących spełnienie warunku wyzwalania

- Pole edycji "Trigger Counter". Parametr ten przesuwa okno pomiarowe o określony czas lub o określoną ilość zdarzeń do przodu osi upływu czasu. Wytłumaczenie tego parametru najlepiej przeprowadzić za pomocą przykładu.

Użytkownik chce zarejestrować analizatorem problem zapisu danych do urządzenia znajdującego się w przestrzeni adresowej pod adresem np. 0x456. Problem polega jednak na tym, że zapis generuje błąd po przepełnieniu liczby np. 3-bajtowej czyli po 16777216 zapisie pod ten adres. Rozmiar bufora niestety nie wystarcza do zarejestrowania wszystkich danych od momentu pojawienia się pierwszej wartości 0x456 na magistrali adresowej. Ilość danych wymaganych do zapisu to w tym przypadku w przybliżeniu 10 próbek na zapis oraz dowolna ilość próbek na zapis pomiędzy zapisami do urządzenia. Załóżmy że wymagana pojemność bufora to miliard próbek. Oczywiście nawet jeżeli rozmiar bufora byłby odpowiedni, to przeglądanie takiej ilości danych jest niewygodne. W tym przypadku warto więc ustawić w analizatorze warunek wyzwalania słowem na adres 0x456 dla sygnałów magistrali adresowej a następnie należy parametr "Trigger Counter" ustawić na wartość 16777216. Kolejnym krokiem jest już tylko uruchomienie cyklu pomiarowego. Analizator po zarejestrowaniu 16777216 warunków wyzwolenia (co w tym przypadku jest 16777216 odwołaniami do urządzenia pod adresem 0x456) rozpocznie właściwy pomiar i po jego zakończeniu dostarczy nam informacje o stanie sygnałów przed i po pojawieniu się 16777216 zapisu.

Poza opóźnieniem pojawienia się właściwego warunku wyzwolenia parametr ten może być również używany do zliczania warunków wyzwalania. Jest to szczególnie przydatne gdy interesuje nas np ilość odwołań pod komórkę pamięci o określonym adresie lub ilość cykli odczytu identyfikowanych przez sygnał np. RD. Aby użyć tej opcji należy parametr "Trigger Counter" ustawić na wartość dostatecznie dużą. Dopuszczalne wartości to 1..4294967295. Po rozpoczęciu pomiaru bieżący stan licznika widoczny będzie na oknie postępu cyklu pomiarowego.

ICS32sx wyzwalanie bitowe

ICS32sx wyzwalanie bitowe Okno to umożliwia skonfigurowanie parametrów wyzwalania bitowego "Analizatora Stanów Logicznych". Dostępne ustawienia to "Tryb Wyzwalania" i "Maska i Wartość" bitowego warunku wyzwalania. Wyzwalanie Bitowe można scharakteryzować jako operacja "OR". Dokładniejsze wyjaśnienie tego pojęcia umieszczono w dalszej części dokumentu.

Sekcje zaznaczone na rysunku:

- Tryb Wyzwalania. Określa metodę interpretacji pojawienia się Bitowego Warunku Wyzwolenia (BWW). Pojawienie się BWW rozumiane jest jako zależność polegająca na uwzględnieniu podczas analizy wyłącznie bitów wejścia pomiarowego dla których odpowiedni bit Maski przyjmuje wartość '1'. Następnie dla każdego z tych bitów porównywany jest stan odpowiedniej linii wejściowej z bitem pola Wartość. Gdy przynajmniej jeden bit ma obie wartości równe generowany jest wewnętrzny warunek zrównania. Następnie zrównanie to, w zależności od Trybu Wyzwalania, interpretowane jest następująco:

<> None. Brak ustawionego warunku wyzwalania.

UWAGA. Gdy Wyzwalanie Słowem również jest ustawione jako None, wówczas analizator nie ma ustawionego warunku wyzwalania. W tym przypadku cykl pomiarowy to jednorazowe zapełnienie bufora wewnętrznego danymi wejściowymi

<> Rising Edge. W każdym cyklu zegarowym sprawdzane jest czy w poprzednim cyklu zegara taktującego system wystąpiło zrównanie się stanu którejkolwiek aktywnej linii wejściowej z wartością ustawioną w odpowiednim bicie parametru Wartość. Jeżeli w poprzednim cyklu brak było zrównania, a w bieżącym cyklu zrównanie to występuje, generowany jest wewnętrzny warunek wyzwolenia

<> Falling Edge. Podobnie jak w przypadku Rising Edge, z tą różnicą, że wewnętrzny warunek wyzwolenia generowany jest gdy w poprzednim cyklu zegarowym było zrównanie, a w bieżącym cyklu zegarowym zrównanie to już nie występuje

<> Level. Wewnętrzny warunek wyzwolenia generowany jest za każdym razem gdy występuje zrównanie się któregokolwiek z aktywnych bitów.

Domyślnie przyjęte jest, że ustawienie Trybu Wyzwalania na np. Rising Edge polega na oczekiwaniu na pojawienie się stanu '0' do '1' na aktywowanej Maską linii wejściowej Analizatora. W tym przypadku przyjęto zasadę, że np. narastające zbocze zdefiniowane jest jako stan określony zależnością: (a) brak pojawienia się warunku wyzwolenia, (b) pojawienie się warunku wyzwolenia. Jak widać, nie na bitach ale na wewnętrznej linii warunku wyzwolenia pojawia się zbocze narastające. Problem nie istnieje w przypadku gdy bit Maski ma aktywne tylko jedno pole. W przypadku większej ilości aktywnych pól może pojawić się sytuacja: Ustawione mamy dwa warunki bitowego wyzwalania na sygnały WR i RD. W przypadku gdy którykolwiek z nich przyjmie wartość '0' generowany jest warunek wyzwolenia. Załóżmy, że sygnały WR i RD przyjmują wartość '0' ale tylko na jeden cykl pomiarowy. Przyjmijmy również, że w jednym cyklu oba sygnały są nieaktywne (oba '1'), w drugim cyklu aktywny jest tylko sygnał WR, w trzecim cyklu aktywny jest tylko sygnał RD, a w czwartym cyklu sygnały te pozostają nieaktywne. W drugim i trzecim cyklu pojawiły się dwa stany różnych sygnałów które generują wewnętrzny sygnał warunku w postaci '0110', gdzie '0' oznacza brak warunku wyzwolenia, a '1' oznacza, że warunek wyzwolenia wystąpił. Analizując otrzymany wynik łatwo jest stwierdzić, że w tym przypadku zamiast dwóch zboczy tak naprawdę pojawia się wyłącznie jedno zbocze narastające. - Numer bitu w danym porcie

- Maska Wyzwalania Bitowego. Graficzny dostęp do poszczególnych bitów Maski

- Wartość Wyzwalania Bitowego. Graficzny dostęp do poszczególnych bitów Wartości

- Nazwa Portu. Składa się z przynajmniej jednego członu (nazwy podstawowej) zawierającego 'P', numer portu i numer bitu w porcie. W przypadku gdy użytkownik zdefiniował sygnał bitowy i nadał mu nazwę, nazwa ta pojawia się obok nazwy podstawowej

- Maska Wyzwalania bitowego. Reprezentacja liczbowa

- Wartość Wyzwalania Bitowego. Reprezentacja liczbowa

UWAGA. Graficzną reprezentację Maski i Wartości można zmieniać bez klikania myszą a jedynie przesuwaniem nad ikonami kursora myszy. W tym celu należy podczas tej operacji wcisnąć "Lewy Ctrl".

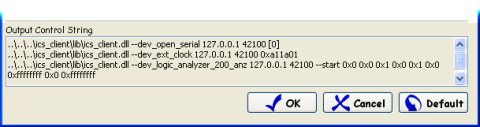

ICS32sx konfiguracja

Okno to umożliwia skonfigurowanie analizatora do pracy z zadanymi parametrami i o określonych wartościach detekcji warunków wyzwalających. Okno składa się z wielu zakładek, których wspólną dolną część stanowi pole zawierające trzy polecenia dla wersji konsolowej urządzenia. Szczegółowe wyjaśnienie zasady działania wersji konsolowej zostało opisane w dokumencie opisującym ogólną zasadę działania urządzenia "In Circuit Spy". Ogólnie program graficzny jest w tym przypadku jedynie nakładką na wersję konsolową programu. Dodatkowo, w tym przypadku aby zminimalizować czas wykonywania polecenia, parametry przekazywane do aplikacji konsolowej są w tym przypadku przekazywane jako łańcuch znaków bezpośrednio do biblioteki "dll". Dzięki temu czas potrzebny na przekazanie polecenia do aplikacji konsolowej został zredukowany prawie stukrotnie i wynosi obecnie pojedyncze milisekundy na rozkaz.

Wygląd części wspólnej zakładek konfiguracyjnych został przedstawiony na rysunku:

Okno zostało wyposażone w przyciski:

- OK. Zatwierdza wprowadzone zmiany i zamyka okno

- Cancel. Anuluje wprowadzone zmiany i zamyka i zamyka okno

- Default. Przywraca ustawienia domyślne. Zmianę ta należy zaakceptować lub odrzucić przyciskami OK i Cancel

Okno konfiguracyjne składa się z wielu zakładek. Opis każdej z nich został umieszczony w następujących miejscach:

- Konfiguracja połączenia

- Konfiguracja zegarów

- Konfiguracja wyzwalania - ustawienia ogólne

- Konfiguracja wyzwalania - wyzwalanie bitowe

- Konfiguracja wyzwalania - wyzwalanie słowem

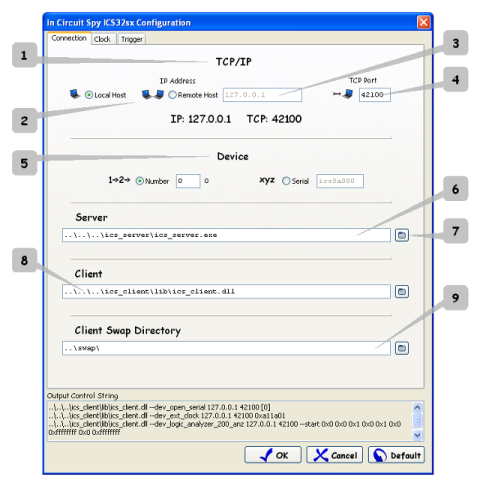

ICS32sx polaczenia

Okno to umożliwia skonfigurowanie systemowych ustawień Analizatora Stanów Logicznych. Skonfigurowane mogą zostać parametry takie jak połączenie sieciowe, wybór urządzenia i ścieżki dostępu do aplikacji konsolowych i katalogu wymiany

Sekcje zaznaczone na rysunku:

- Sekcja TCP/IP. W niej ustawia ustawiane są właściwości połączenia sieciowego

- Lokalizacja serwera:

<> Local Host. Ustawienie domyślne. Server zloazlizowany jest na tym samym komputerze co aplikacjia graficzna. Podczas pomiaru oprogramowanie samo okresla czy serwer jest uruchomiony. Jeżeli nie otwiera w nowej konsoli instancję serwera skonfigurowanego do współpracy z bieżącą sesją pomiarową

<> Remote Host. Serwer jest dostępny na komputerze o podanym adresie IP. W tym przypadku należy pamiętać aby przed rozpoczęciem pomiaru uruchomić serwer z ustawieniem odpowiedniego dopuszczalnego przychodzącego adresu IP. W tym przypadku jest to IP komputera na którym znajduje się aplikacja graficzna analizatora

- Adres IP komputera na którym znajduje się uruchomiony serwer

- Adres TCP który zostanie wykorzystany do komunikacji pomiędzy aplikacją kliencką a serwerem

- Sekcja Device. Odpowiedzialna za wybór urządzenia. Dostępne opcje:

<> Number. Z listy dostępnych urządzeń wybierane jest urządzenie 0, 1, 2, itd. Konfiguracja listy zależy od portów USB w jakie zostało wpięte urządzenie

<> Serial. W liście dostępnych urządzeń wybierane jest urządzenie o podanym numerze seryjnym. Opcja ta jest szczególnie przydatna przy pracy z wieloma urządzeniami ICS

- Server. Ścieżka dostępu do serwera

- Jeden z wielu przycisków umożliwiających zmianę ścieżki dostępu do danego zasobu

- Client. Ścieżka dostępu do aplikacji konsolowej analizatora (klienta)

- Swap. Katalog wymiany. W nim zapisywane są wyniki pośrednie pomiaru. Katalog ten jest otwierany przy pierwszym pomiarze. Dane zapisywane w katalogu posiadają w nazwie datę i czas utworzenia dzięki czemu w łatwy sposób użytkownik może przeanalizować wcześniejsze pomiary bez konieczności każdorazowego zapisywania wyników. Katalog ten należy opróżniać według własnego uznania

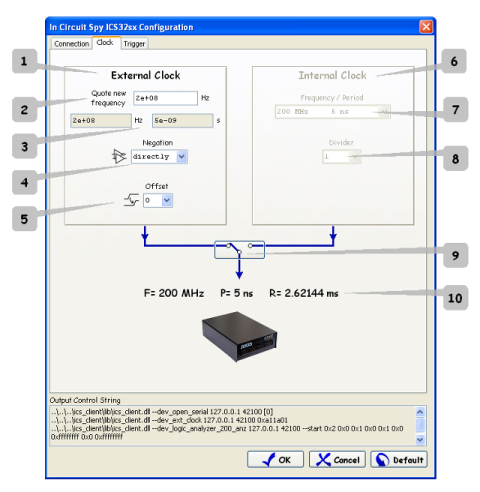

ICS32sx konfiguracja zegara

Okno to umożliwia skonfigurowanie głównego zegara systemowego urządzenia. Częstotliwość zegara wyznacza ilość próbek zapisywanych w jednostce czasu. Zegar ten może być ustawiony do pracy w dwóch głównych trybach:

- External Clock. Zegar taktujący analizator podawany jest na wejście urządzenia. Wszystkie zapisy próbek odbywają się na zboczu narastającym lub opadającym sygnału z możliwością przesunięcia fazy sygnału zegarowego. Graniczne częstotliwości ograniczone są jedynie przez częstotliwość maksymalną wynoszącą 200MHz. W praktyce jednak, ze względu na różne czynniki powodujące złe dopasowanie linii łączących, stabilna maksymalna częstotliwość pracy wynosi często 100MHz. Podczas testowania gotowego urządzenia, zanim opuści ono linię montażową, przeprowadzany jest na nim test polegający na naprzemiennym podawaniu zer i jedynek na wszystkie wejścia pomiarowe synchronicznie do zegaru taktującego wynoszącego nie mniej niż 200MHz. Przy takich częstotliwościach często sygnał zegarowy wymaga przesunięcia fazy co również zostało zaimplementowane w urządzeniu jako opcja "Offset"

- Internal Clock. Sygnał zegarowy taktowany jest wewnętrznym programowalnym modułem zegarowym. Częstotliwość graniczna urządzenia mieści się w granicach 200MHz do w przybliżeniu 100Hz. W tym przypadku ustawiane są dwie wartości modułu zegarowego. Częstotliwość taktowania i podzielnik. Obie te opcje zostały opisane w dalszej części dokumentu.

Zakładka konfiguracji zegara systemowego została przedstawiona na rysunku:

- Sekcja External Clock. W niej ustawiane są właściwości taktowania urządzenia zewnętrznym sygnałem zegarowym

UWAGA. W tym trybie pracy urządzenie nie wie jaka jest częstotliwość sygnału zegarowego. Dodatkowo, częstotliwość ta może zmieniać się w czasie trwania cyklu pomiarowego. Dlatego też użytkownik musi wprowadzić tą częstotliwość ręcznie, a jej wartość potrzebna jest urządzeniu jedynie do wyznaczania zależności czasowych potrzebnych do przeliczania okresu i częstotliwości przy wyświetlaniu stanu kursorów oraz do zapisu wartości zegara dla plików opisu sprzętu takich jak Verilog i VHDL

- Quote new frequency. Pole edycji umożliwiające wprowadzenie częstotliwości zegara taktującego urządzenie

- Kontrolne pola edycji, tylko do odczytu, przedstawiające częstotliwość i okres sygnału zegarowego wyliczone na podstawie wartości podanej przez użytkownika

- Negation. Pole umożliwiające wprowadzenie sygnału zegarowego bezpośrednio do urządzenia lub jako zanegowany sygnał taktujący

- Offset. Określenie przesunięcia fazowego sygnału zegarowego. Możliwe jest ustawienie jednej z 16 wartości.

UWAGA. Opcje "Negation" i "Offset" wpływają znacząco na przesunięcie zboczy zatrzaskujących sygnału zegarowego względem sygnałów mierzonych podawanych na wejścia pomiarowe. Opcja ta z reguły stosowana jest przy częstotliwości pracy większej niż 50MHz. Jedną z 32 wartości (Negation = 2 * Offset = 16) należy dobrać eksperymentalnie. Dostrajanie polega na dobraniu takich ustawień przy których składowe sygnałów badanych magistral nie są przesunięte względem siebie na wykresie

- Sekcja Internal Clock. W niej ustawia ustawiane są właściwości taktowania urządzenia wewnętrznym sygnałem zegarowym

- Frequency/Period. Opcja ustawiająca częstotliwość pracy programowalnego modułu pomiarowego

- Divider. Podzielnik częstotliwości ustalanej w polu "Frequency/Period".

UWAGA. W wersji podstawowej dostarczonego oprogramowania użytkownik ma możliwość wybrania jednej z kilkunastu dostępnych opcji znajdujących się w polu "Frequency/Period". Projektanci urządzenia zdecydowali się jednak odtajnić informacje, które znacząco zwiększą zakres używanych częstotliwości. Jest to przydatne szczególnie w przypadku, gdy urządzenie "In Circuit Spy" w trybie pracy "Analizator Stanów Logicznych" jest używane jako generator sygnału zegarowego. Szczegółowe informacje podano w dalszej części dokumentu

- Wybór trybu pracy urządzenia. Dostępne konfiguracje to "External Clock" i "Internal Clock"

- Podsumowanie parametrów zegara taktującego wewnętrzną logiką urządzenia. Podsumowanie stanowią trzy wartości:

<> F. Częstotliwość zegara taktującego

<> P. Okres zegara taktującego

<> R. Zakres. Przedział czasu jaki objęty został pomiarem. Jest to wartość wyliczona na podstawie wzoru "Okres zegara taktującego" * "Pojemność bufora urządzenia"

UWAGA. Informacja dla użytkowników zaawansowanych. Wewnętrzny sygnał zegarowy jest generowany za pomocą układu scalonego ICS307-02. Dokumentacja do układu oraz do kalkulatora dostępna w sieci na stronach producenta.Wartości wyświetlane w oknie "Frequency/Period" generowane są na podstawie zawartości pliku clock.ipc znajdującego się w katalogu głównym aplikacji graficznej. Format pliku to dwie kolumny zawierające następujące informacje:

- Kod wymaganej częstotliwości wygenerowany za pomocą wzoru znajdującego się w dokumentacji lub za pomocą kalkulatora dostępnego na stronie producenta układu. Jest to pole obowiązkowe Format pola to liczba heksadecymalna o postaci "0x------". Należy pamiętać, że nie wszystkie możliwe kombinacje parametrów układu generują stabilny sygnał zegarowy. Dodatkowe informacje dostępne w dokumentacji układu

- Częstotliwość pracy układu. Pole opcjonalne. Wartość częstotliwości podawana w polu wyboru programu wyliczana jest na podstawie Kodu częstotliwości.

W celu obliczenia kodu częstotliwości wymagane są informacje:

- Clk2 Output - REF

- Output Duty Cycle Configuration - 1 (CMOS)

- Crystal Load Capacitance - "10"

- Input Frequency - 10MHz

- Output - Lowest Jitter